# EGC221 Class Notes 4/26/2023

**Baback Izadi** Division of Engineering Programs bai@engr.newpaltz.edu

## Finite State Machines (FSM)

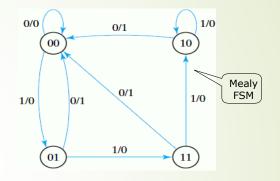

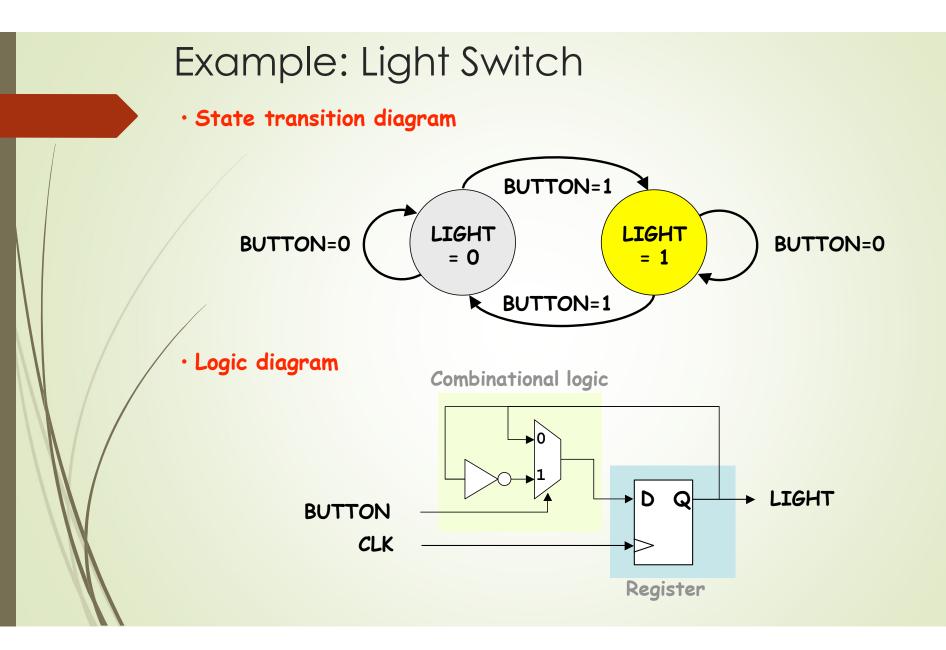

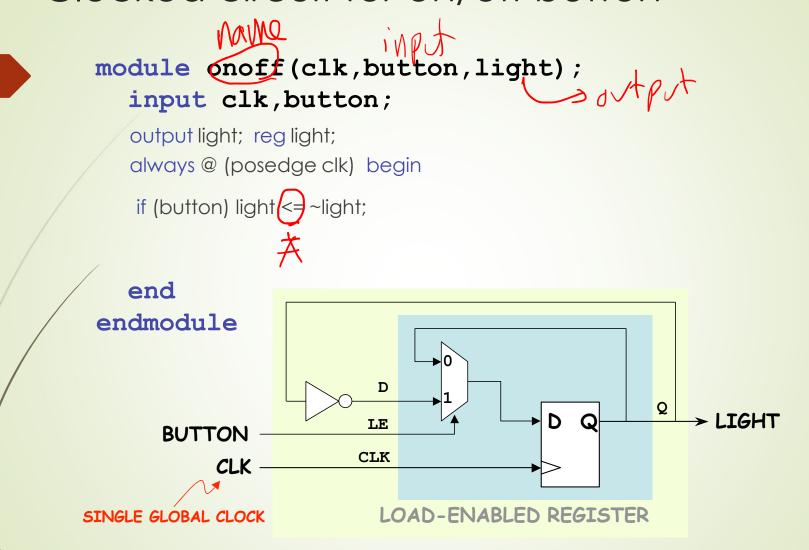

- State diagrams are representations of Finite State Machines (FSM)

- Mealy FSM

- Output depends on input and state

- Output is not synchronized with clock

- can have temporarily unstable output

- Moore FSM

- Output depends only on state

#### Finite State Machines

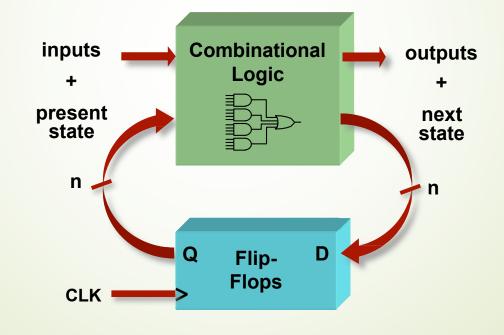

- Finite State Machines (FSMs) are a useful abstraction for sequential circuits with centralized "states" of operation

- At each clock edge, combinational logic computes *outputs* and *next state* as a function of *inputs* and *present state*

####

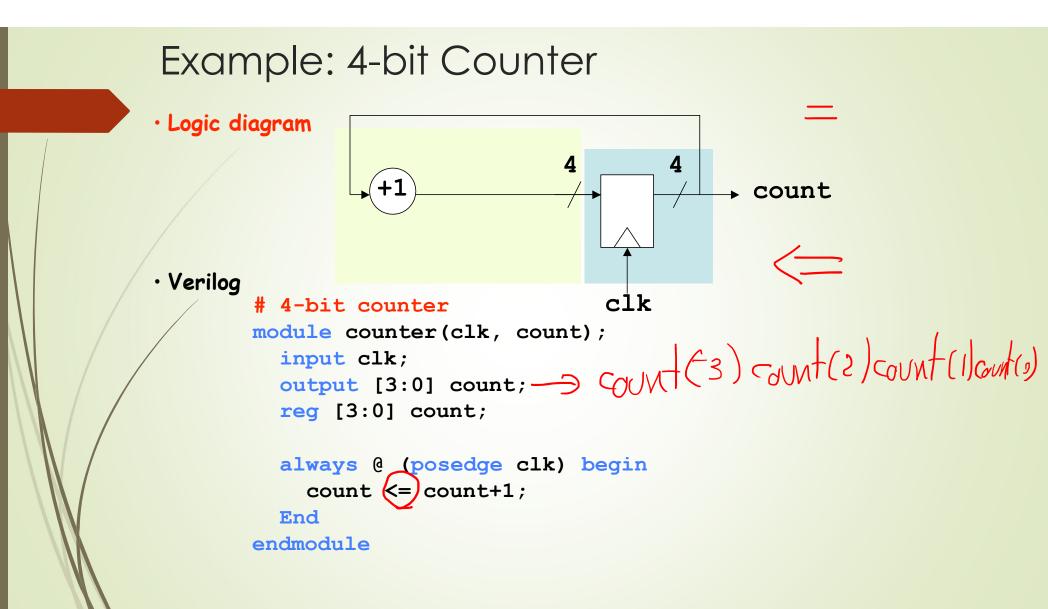

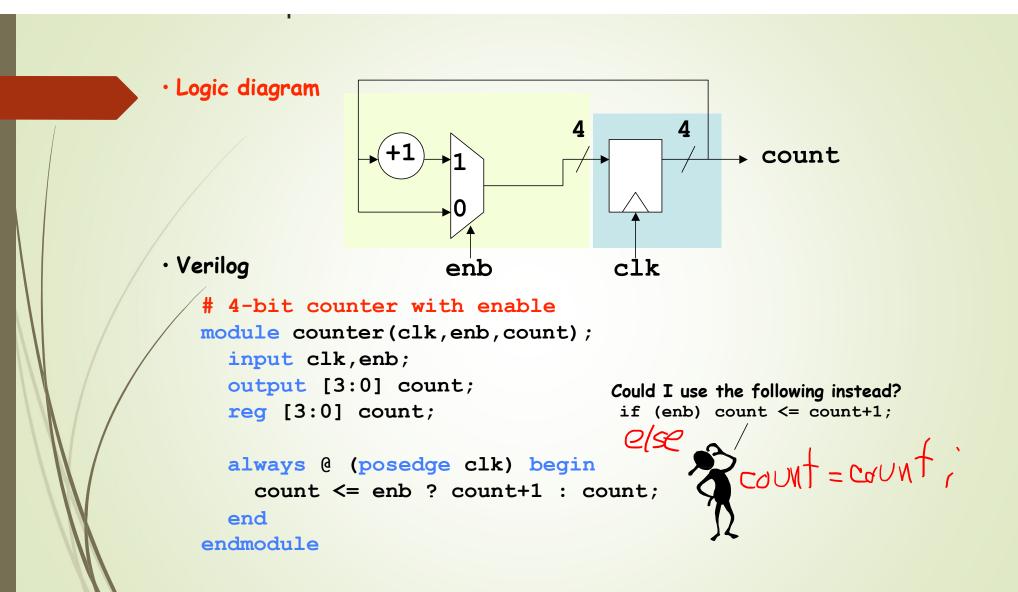

#### EXUITIPIE. 4-DII COUTTET

· Logic diagram 4 → count • Verilog enb clk clr # 4-bit counter with enable and synchronous clear module counter(clk,enb,clr,count); input clk,enb,clr; output [3:0] count; reg [3:0] count; always @ (posedge clk) begin count <= clr ? 4'b0 : (enb ? count+1 : count);</pre> end endmodule

### 4-bit Shift Register with Reset

```

module srg 4 r v (CLK, RESET, SI, Q,SO);

input CLK, RESET, SI;

output [3:0] Q;

output SO;

reg [3:0] Q;

assign SO = Q[3];

Asynchronous input

always@(posedge CLK or posedge RESET)

if (RESET)

Q <= 4'b0000;

S

else

Q \le \{Q[2:0], SI\};

end

\sim

endmodule

```

```

4-bit Binary Counter with Reset

module count 4 r v (CLK, RESET, EN, Q, CO);

input CLK, RESET, EN;

output [3:0] Q;

output CO;

reg [3:0] Q;

assign CO = (count == 4'b1111 && EN == 1'b1) ? 1 : 0;

always@(posedge CLK or posedge RESET)

begin

if (RESET)

Q <= 4'b0000;

else if (EN)

Q \le Q + 4'b0001;

end

endmodule

```

You are to design a 4-bit counter with the following inputs and functionality:

- Load (Id): if activated, count will be loaded from D\_in [3:0] •

- Mode: if 0, counter counts up. Otherwise, it will count down.

- Clear (clr): If activated, count will be 0

- Clear (cir). If activated, count the Clock 1 Hz is generated from the previous exercise.

Complete the following code and implement it on the FPGA board.

Ld = 1  $Q_3 - Q_0 \qquad D_3 - D_0$

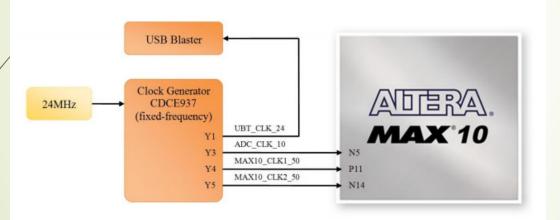

| Signal Name   | FPGA Pin No. | Description                          |

|---------------|--------------|--------------------------------------|

| ADC_CLk_50    | PIN_N5       | 10 MHz clock input for ADC (Bank 3B) |

| MAX10_CLK1_50 | PIN_P11      | 50 MHz clock input (Bank 3B)         |

| MAX10_CLK2_50 | PIN_N14      | 50 MHz clock input (Bank 3B)         |

| Device family                                        | Show in 'Available devices' li | st |

|------------------------------------------------------|--------------------------------|----|

| Family: MAX 10 (DA/DF/DC/SA/SC)                      | Package: Any                   | •  |

| Device: All                                          | Pin count: Any                 | •  |

| Target device                                        | Core speed grade: Any          | •  |

| ○ Auto device selected by the Fitter                 | Name filter:                   |    |

| Specific device selected in 'Available devices' list | Show advanced devices          |    |

| Other: n/a                                           |                                |    |

#### Available devices:

| Name          | Core Voltage | LEs         | Total I/Os  | GPIOs          | Memory Bits     | Embedd           | led multiplier ? ^ |              |

|---------------|--------------|-------------|-------------|----------------|-----------------|------------------|--------------------|--------------|

| 0M50DAF484C7G | 1.2V         | 49760       | 360         | 360            | 1677312         | 288              |                    |              |

| <b>C</b>      |              |             |             |                |                 |                  | >                  |              |

|               |              |             |             |                |                 |                  |                    |              |

| USB Stealer   |              |             | PGA         |                |                 |                  |                    |              |

|               | FT245        |             |             | -              | -               | Gad              |                    |              |

|               |              |             | MA          | Xº 1           | 0               | 1070AA864MB (105 |                    |              |

| -             | Dight        | 107 .       | 101450      | DAEARA         |                 | Accelerated      |                    |              |

| Arburg He     |              |             |             | DAF484         |                 |                  |                    |              |

|               | Annual       | -1 AD       | c           |                |                 | SCA10            | he)                |              |

| 1997          |              |             |             |                | Determined + 32 |                  |                    |              |

|               |              |             | +48 ×70     | 110            | Sig             | nal Name         | FPGA Pin No.       | Description  |

|               |              | 8888        | 888         |                | KE'             |                  | PIN_B8             | Push-button[ |

|               |              | 1-Segment 5 | Septery all | ******         | KE              | Y1               | PIN_A7             | Push-button[ |

|               |              |             | LED x10     | <b>BEBBBBB</b> | 1888            |                  |                    | ·            |

# BoardDevice NameDE10-LiteMAX 10:<br/>10M50DAF484C7GPin Assignment

| Signal Name | FPGA Pin No. | Description     |

|-------------|--------------|-----------------|

| SW0         | PIN_C10      | Slide Switch[0] |

| SW1         | PIN_C11      | Slide Switch[1] |

| SW2         | PIN_D12      | Slide Switch[2] |

| SW3         | PIN_C12      | Slide Switch[3] |

| SW4         | PIN_A12      | Slide Switch[4] |

| SW5         | PIN_B12      | Slide Switch[5] |

| SW6         | PIN_A13      | Slide Switch[6] |

| SW7         | PIN_A14      | Slide Switch[7] |

| SW8         | PIN_B14      | Slide Switch[8] |

| SW9         | PIN_F15      | Slide Switch[9] |

| Signal Name | FPGA Pin No. | Description |

|-------------|--------------|-------------|

| LEDR0       | PIN_A8       | LED [0]     |

| LEDR1       | PIN_A9       | LED [1]     |

| LEDR2       | PIN_A10      | LED [2]     |

| LEDR3       | PIN_B10      | LED [3]     |

| LEDR4       | PIN_D13      | LED [4]     |

| LEDR5       | PIN_C13      | LED [5]     |

| LEDR6       | PIN_E14      | LED [6]     |

| LEDR7       | PIN_D14      | LED [7]     |

| LEDR8       | PIN_A11      | LED [8]     |

| LEDR9       | PIN_B11      | LED [9]     |

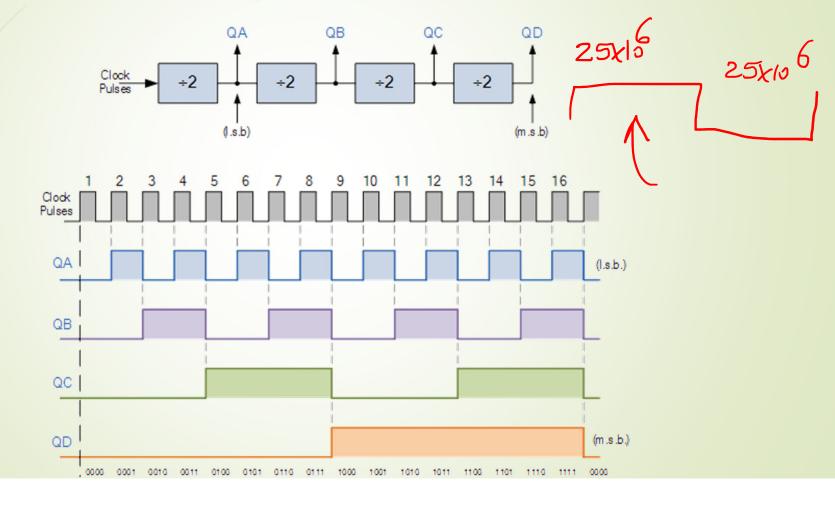

#### **Exercise 1:** Divide-by-N Circuit:

Design, simulate, and build a Divide-by-N circuit that will divide the on board clock from 50 MHz down to ~1 Hz. The basic principle is as follows:

```

//The goal of this always procedural block is to generate 1Hz clock from a

//50MHz clock that is used in the Altera FPGA board.

module Divide_by_50M_counter(clr,clk,clk_1Hz);

input clr,clk;

25,000,000

output clk_1Hz;

reg clk_1Hz =1'b0;

integer counter_50M =0;

always @(posedge clk, posedge clr)

begin

if (clr)

counter_50M <= 0;

else if (counter_50M < 25000000)

begin

counter_50M <= counter_50M + 1;</pre>

end

else if (counter_50M == 25000000)

begin

clk 1Hz <= !clk 1Hz;

counter_50M <=0;</pre>

end

end

endmodule

```

module up\_down\_counter(mode,clr,ld,D\_in,clk,count,clk\_1Hz);

() so up to = > > 4 inpts output

input mode, clr, ld, clk; input [3:0] D\_in; output clk\_1Hz; output [3:0] count; reg [3:0] count; reg clk\_1Hz = 1'b0; integer counter\_50M =0;  $\int \int \int \int \int \int V e V - \int \int \int \int \partial Q e V de V$

//If "ld =1" we load the external data through D\_in[3:0], if mode is active

// it will be counting up and if mode is inactive it will count down.

always @(posedge clk\_1Hz, posedge clr) -loadbesin iB(mode) counte count - 1; . if (clr)

count <=0; else if (ld) count <= D\_in[3:0],

endmodule